XCZU47DR

產(chǎn)品型號(hào)

AXW22價(jià)格

¥58000.00

XILINX zynq7035 7000 FPGA開發(fā)板 PCIE 光纖 HDMI XC7Z035 AX7Z035B

ALINX黑金Xilinx Zynq UltraScale+ MPSoC PCIE AI FPGA開發(fā)板 ZU5EV XCZU5EV AXU5EVB-P

Xilinx Zynq UltraScale+ MPSoC AI 100G光纖 HPC FPGA開發(fā)板 ZU19EG XCZU19EG Z19

Xilinx Zynq UltraScale+ MPSoC AI 智能 FPGA開發(fā)板 ZU2CG XUZU2CG AXU2CGB

自適應(yīng)射頻無線電開發(fā)平臺(tái) Zynq UltraScale+ RFSoC FPGA 開發(fā)板 XCZU49DR 雷達(dá)通信

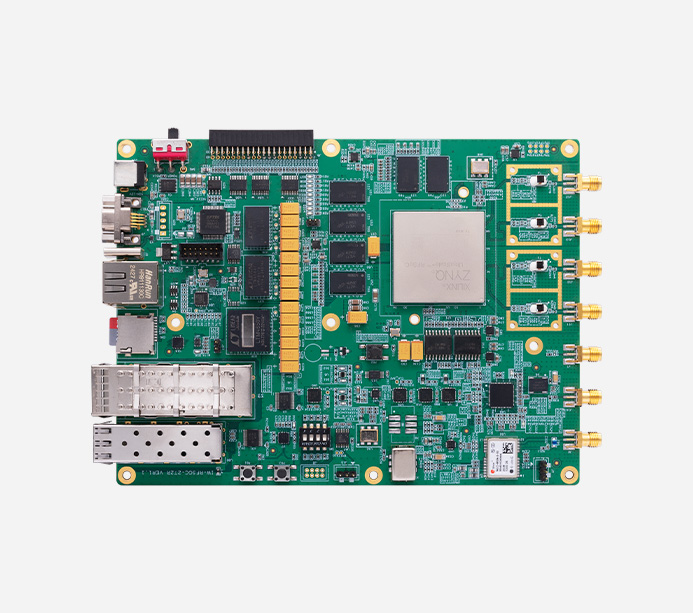

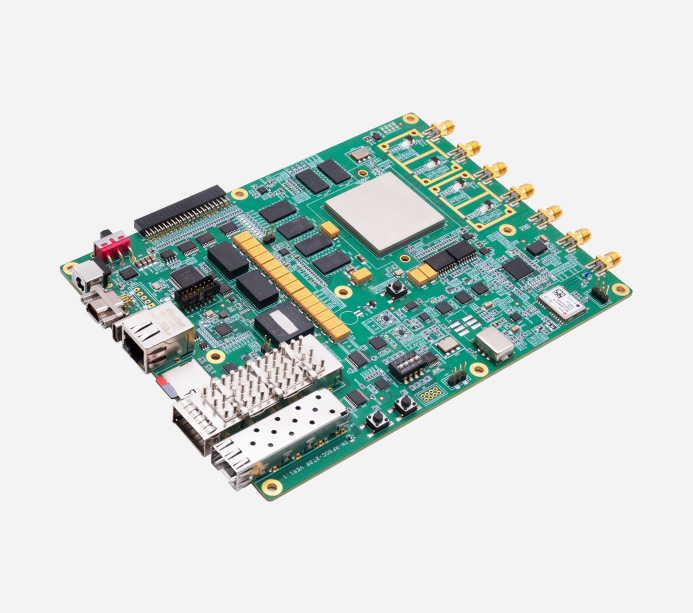

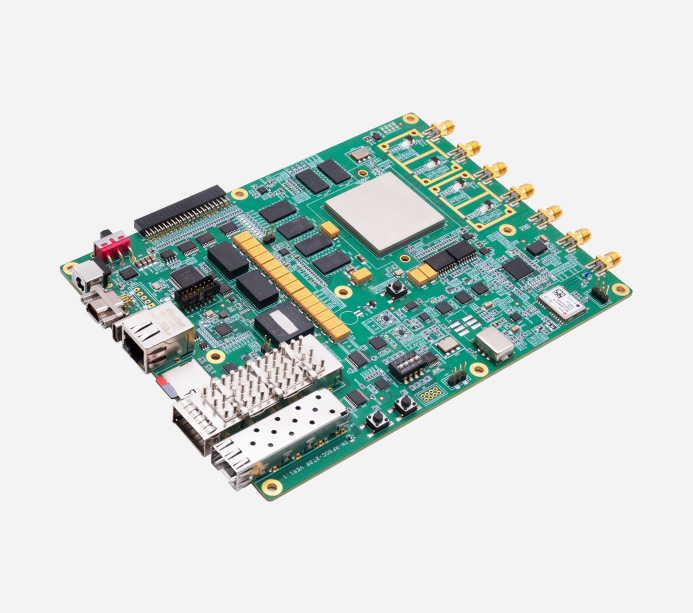

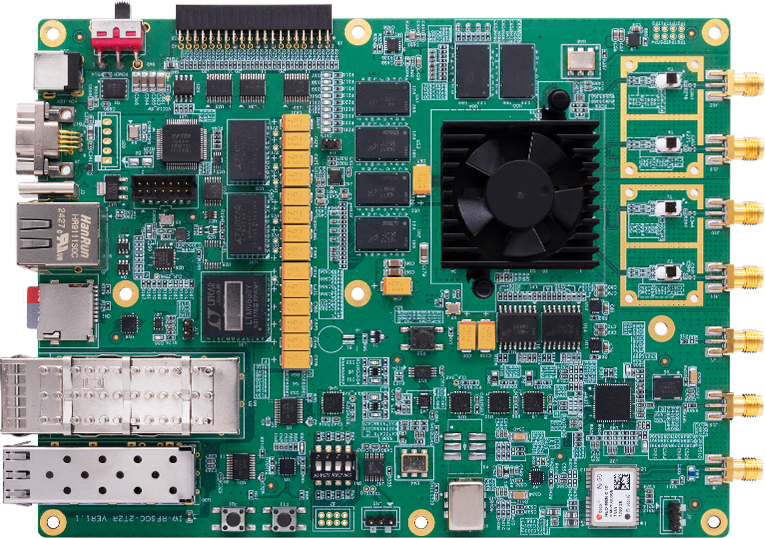

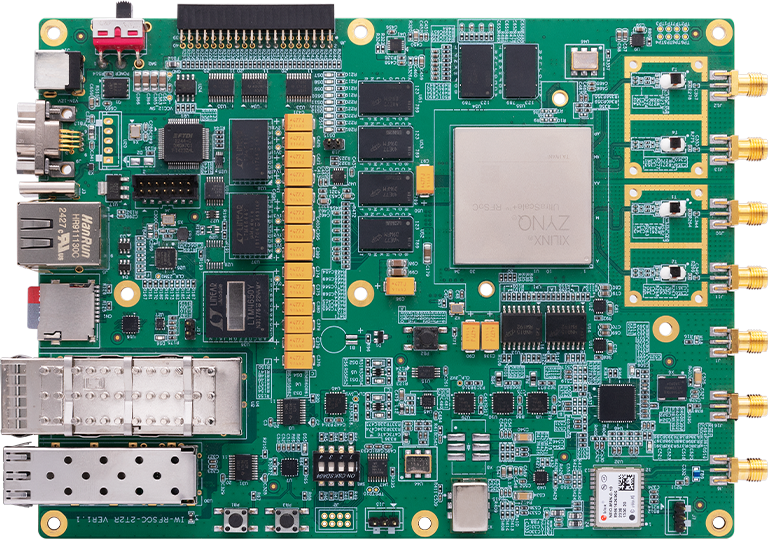

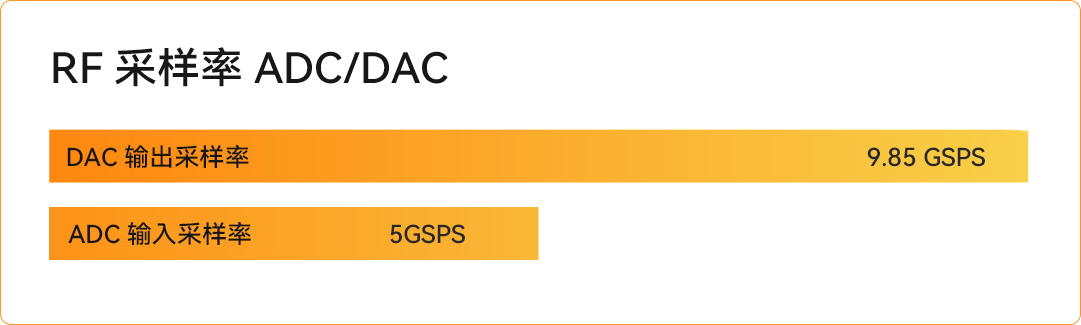

AXW22 采用 AMD Zynq UltraScale+ RFSoC Gen3 系列 ZU47DR 芯片, 支持 2 路14 位 RF-ADC 輸入,最大采樣率可達(dá) 5GSPS,2 路 14 位 RF-DAC 輸出,最高采樣率可達(dá) 9.85GSPS

高端射頻信號(hào)芯片

Logic Cells

2 路 14bit ADC

2 路 14bit DAC

高速數(shù)據(jù)傳輸接口

光纖接口

采用 ?Zynq UltraScale+ RFSoC XCZU47DR FPGA? 芯片,集成 Quad ARM Cortex-A53 和 Dual ARM Cortex-R5F 處理器,支持實(shí)時(shí)操作系統(tǒng) (RTOS)與 Linux 并行運(yùn)行?

多核處理器

LUTs

DSP Slices

PS DDR4

PL DDR4

QSPI FLASH

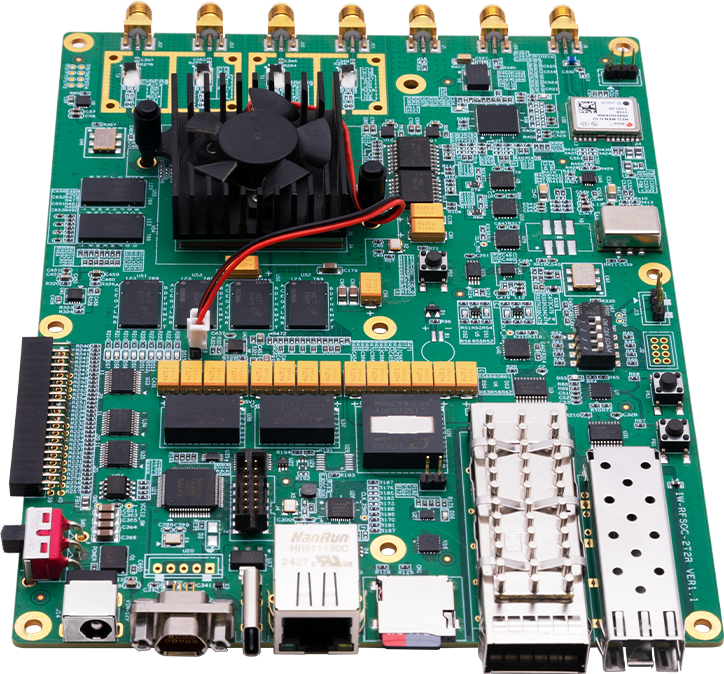

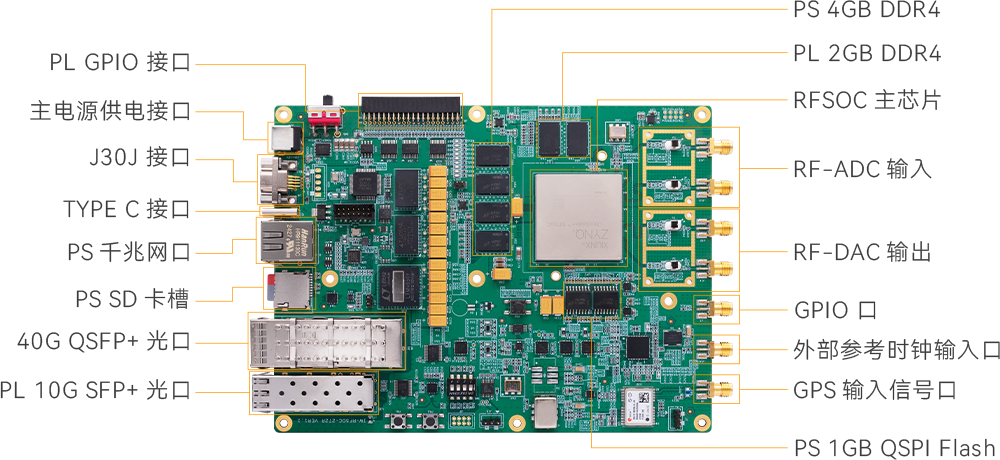

RF發(fā)送和RF接收端口通過高性能SMA側(cè)插 RF 連接器對(duì)外連接,以Zynq UltraScale+ RFSOC作為核心處理系統(tǒng),具有豐富的外設(shè)接口用于匹配信號(hào)處理的外圍控制信號(hào)傳輸。AXW22板載40Gbps QSFP 連接器提供光口,10Gbps SFP光口,可與模擬和數(shù)字轉(zhuǎn)換并行地有效處理高速數(shù)據(jù)

支持 2 路 14 bit ADC 5GSPS 輸入,2 路 14 bit DAC 9.85GSPS 輸出, 單端信號(hào)輸入輸出,通過巴倫器件進(jìn)行差分單端互轉(zhuǎn)功能,完成對(duì)數(shù)據(jù)的發(fā)送和接收,并且VCM 信號(hào)也引出至 TP,方便用戶調(diào)節(jié)共模電壓

Zynq UltraScale+ RFSoC 異構(gòu)計(jì)算架構(gòu),包括完整的 ARM 處理子 系統(tǒng)、FPGA 架構(gòu),以及 RF 信號(hào)鏈中的完整模數(shù)可編程性,提供 一個(gè)完整的單片軟件定義無線電平臺(tái)

·2 路 14-bit 射頻直采 ADC/DAC?

·支持多板級(jí)聯(lián)同步,滿足大規(guī)模系統(tǒng)(雷達(dá)陣列等)需求

·直接射頻采樣技術(shù)替代傳統(tǒng)模擬轉(zhuǎn)換,降低功耗與成本

·點(diǎn)芯片級(jí)集成 ADC/DAC,消除 JESD204B 接口需求,減少信號(hào)延遲

·RFSoC將射頻采樣、FPGA和處理器集成,簡(jiǎn)化硬件架構(gòu),降低功耗和體積

·RF 采樣器件消除了 JESD204B 高速串行接口的復(fù)雜性,減少計(jì)算資源

· 采用 1 通道 40G QSFP VITA 66.4 光纖接口和1通道10G SFP光纖接口來有效 地卸載數(shù)據(jù)

芯片型號(hào)

XCZU47DR-2FFVE1156I

芯片 CPU

Quad-core Arm CortexA53 MPCore

Dual-core Arm Cortex R5F MPCore

14 bit 2.5GSPS RF-ADC

8

14 bit 9.85GSPS RF-DAC

8

Decimation/ interpolation

1x, 2x, 3x, 4x, 5x, 6x, 8x, 10x, 12x, 16x, 20x, 24x, 40x

GTY/GTR

PL 端 GTY 8/PS 端 GTR 4

System Logic Cell

930K

CLB LUTs

425K

Max.Dist.RAM

13.0Mb

Total Block RAM

38.0Mb

UltraRAM

22.5Mb

DSP Slices

4272

PCIe Gen4 x8

2

內(nèi)存

PS 端 4 片 1GB DDR4 共 4GB

PL 端 2 片 1GB DDR4 共 2GB

板卡供電

2.5mm 圓頭電源插座(DC +12V)

PS 端接口

2x 128MB QSPI flash 固化配置文件

1x JTAG 調(diào)試接口

1x 10/100/1000 Ethernet RGMII (RJ45) 網(wǎng)口

1x Mircro SD Card

PL 端接口

2 路 ADC (14-bit 、5GSPS) 端口

2 路 DAC (14-bit、9.85GSPS) 端口

1x QSFP+ 40G 光口

1x SFP+ 10G 光口

1 路 I2C 接口的 EEPROM

GPS 接口(接口形式:側(cè)插SMA連接器)

1 路 SPI 接口和 1 路 GPIO(接口形式:J30J連接器)

36x GPIOs(接口形式:2.0mm間距彎插排座)

1x RS232接口(接口形式:2.0mm 間距彎插排座) IO

8x LEDs

環(huán)境溫度

工作時(shí) -40℃~85℃

FPGA 開發(fā)板

1 塊

散熱風(fēng)扇

1 個(gè)

SD卡

1個(gè)

網(wǎng)線

1 根

SMA 線

4 根

電源適配器

1 個(gè)

資料 U 盤

1 個(gè)

尺寸大小

擴(kuò)展板 180mm x 135mm

XCZU47DR 芯片集成 Quad Cortex-A53 處理器 + 930K 邏輯單元,支持復(fù)雜算法實(shí)時(shí)處理,適用于 5G 基站、雷達(dá)信號(hào)處理等高精度場(chǎng)景

通過 Zynq RFSoC,無線基礎(chǔ)設(shè)施制造商可實(shí)現(xiàn)顯著的占板面積及功耗減少,這對(duì)后期 MIMO 技術(shù)的發(fā)展至關(guān)重要

通過 Zynq RFSoC 中用直接 RF 采樣、高靈活、可重構(gòu)邏輯及軟件可編程性,為信號(hào)生成和信號(hào)分析構(gòu)建高速度的多功能儀器

具有 2 通道 ADC 和 2 通道 DAC,可滿足更大的應(yīng)用需求,能夠在預(yù)警場(chǎng)景下實(shí)現(xiàn)低時(shí)延收發(fā),獲得最佳響應(yīng)時(shí)

通過 Zynq RFSoC 中用直接RF采樣、高靈活、可重構(gòu)邏輯及軟件可編程性,為信號(hào)生成和信號(hào)分析構(gòu)建高速度的多功能儀器

所有出售產(chǎn)品主體保修期為 12 個(gè)月,其中 FPGA 芯片、液晶屏為易損件,不在保修范圍內(nèi)。

所有配件及贈(zèng)品不在保修范圍內(nèi)。

請(qǐng)您補(bǔ)充以下信息,開啟一鍵下載。